First the schematic. I opened it in KiCad V5.0.2 and the symbol for yu uC had to be “Resqued” because you are using old symbols. Are you still using KiCad V4, or have you KiCad V5 mixed up with KiCad libraries from V4 (this happens quite often)?

Then, the overal view of the schematic is quite good, a few small points:

You’ve used the “Earth” symbol instead of the “GND” symbol for GND. These have different meanings and purposes, but for the design of the PCB itself it does not matter, the’re just connected together.

You’ve also used global labels for Vcc. Using the VCC power symbol for Vcc makes your schematic a bit more readable.

You’e used global labels for everything, (I do that too sometimes), for your nex project try to get acquainted with the local and hierarchical labels. The “Getting started with KiCad” manual is a bit out of date, but the reference manuals for the KiCad programs are more up to date, and you probably learn some tricks when reading them.

http://docs.kicad.org/

Then I ran an ERC check, and it gave an error on AVcc.

AVCC of AVR controllers are a real power input, and they need to be connected to VCC. It’s common to add a capacitor to Aref, but not mandatory. If you place it on the schematic (+ PCB) you can always decide later if you want to add it.

I was missing a GND pin. But that’s KiCad’s fault. I find it personally a bit annoying that “Agnd” (Pin 22) is implitly hidden in the schematic. This is a known “fault” though and likely to be handled differently (hopefully better) in KiCad V6.

On any uC board I like to see some choke or inductor on the power supply inputs. This makes almost every uC board more reliable.

Looking at the PCB now. Double sided PCB’s are cheap now, and this is clearly meant to be made by a manufacturer. Youve put quite some effort in a neat layout, putting all the text on the silk screen right etc.

I first ran a DRC:

Pcbnew / Inspect / Design Rules Checker.

If found 2 errors: “Track near Via” near C3 and an “Unconnected pin” which turns out to be a small floating dot of copper under “R4” Silkscreen text.

You should always make sure you have no DRC errors left before having a board manufactured. I moved the via a bit, and then did:

Pcbnew / Edit / Cleanup tracks and via’s.

After this I re-run DRC and there were no more errors (But you still have to change AVCC).

Apart from your AVCC pin it looks like this board will work.

The next biggest thing is the total abence of a GND plane.

I first removed the whole “Earth” net, and then used:

Pcbnew / Place / Zone

to draw a pentagon around your board, connected to the “Earth” net.

After that I clicked on the edge of the zone and pressed “e” to edit it and changed the “Clearance” and the “anti pad clearance” from 0.508 mm to 0.3mm. This makes the zone sneak through all the 0.1" spaced pins and makes a nice solid ground connection.

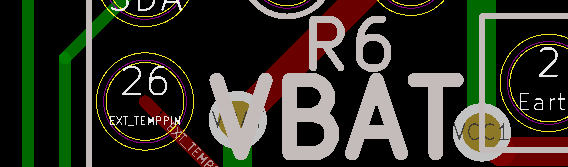

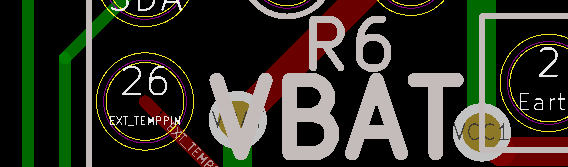

The board now looks like:

I drew a pentagon around the board for the Zone boundary, because KiCad should keep the zone nicely within your board outline.

If it does not and the whole pentagon gets filled, you see it immediately in Pcbnew, or in a Gerber viewer.

The zone is not finished though. Ideally you have a power connector, then a filter on the input power, (Choke + caps), then the voltage regulator, and only then the connection tho the GND (Sorry, “Earth”) net.

When working with GND planes there are a few more wize rules:

- Make them as continuous as possible, no big cutouts for traces.

- Be carefull with mounting holes.

Sometimes you want to keep the GND zone away from mounting holes.

Sometimes you want to connect the GND zone to the mounting holes.

KiCad has some nice mounting holes with included annular ring, with the size of the screws for the mounting holes.

On the schematic I did not notice the reset circuit. It is a bit clearer if you put the reset switch, C6 and R2 close toether on the schematic. Ceramic capacitors (C6) can deliver high peak currents. This puts a lot of war on the switch (it may deliver 10A peak currents, the switch is not made for that) and such high current peaks put a lot of noise in the GND plane (Although both are not very important for the Reset switch).

Finally some small notes:

You put your resistors vertically on the PCB. This way they easily get bent, or misaligned. It “looks better” if you lay the resistors flat on the PCB. With analog circuits this is often also very handy because you can route a number of traces under the resistors.

If you work with a coarse grid during the component placement, the board also loos neater. A coarse grid also makes it very easy to fix the locations for your mounting holes and board outline.

Currently I measure approx 1.56" * 2.21", or 39.62mm * 56.13mm for the outline. I do not know if this on purpose (I did notice the edges are perfectly square to each other), or accidentally, but with the use of a coarse grid it’s easy to make nice round numbers.

LM35 is a relatively expensive temperature sensor (EUR 5). Compare that with for example the MCP9700 ( 23ct).

C1 is most likely the highes part on the PCB. If you make a bit of room around it, you can bend it over and lay it flat on the PCB. (Possibly with some glue).

Keep a bit of area clear around the reset switch, so you do not touch other components (C6, R2) when you try to push the reset switch.

Everything on this board is relatively low power, but still I like to see some fatter traces for the Vcc net. This will also give you some practice for working with different trace widths.

You can do this with:

1). Pcbnew / Setup / Design Rules / [Add]

2). Add a name, for example “Thick” & OK.

3). Change track width and clearances, and via settings.

4). Select your “Thick” net class in the right dropdown box.

5). Move all the “power” nets to the right with the [ >>> ] button.

You should also change the “Via Drill” and “Via Dia” of the default net.

0.4mm drills are very thin and break easily, and are therefore more expensive to manufacture. Drills of 0.6mm or thicker are generally OK.

This is what I made of it, (but sizes ar a bit arbitrary).

If you now run the DRC again, there should be errors, but there are not.

Apparently the design rules for the widht of the tracks are not checked in the DRC.

You can update the track widths of existing tracks with:

Pcbnew / Edit / Edit all Tracks and Vias / Global Edition Option: / (*) Set all tracks and vias to their Netclass value / [ OK ]

Now you can see that the thickness of the tracks of several nets have been updated where possible, and keep a small thin section if the thick line does not fit (For example Vcc net between pins 3 and 4 of the AVR.)

You can easily clean them up by drawing a new line around the AVR pins.

Silk screen text placed over Via’s gets easily distorted. I recommend either moving the via or the text.

And finally, never forget to admire your own craftsmanship

Look at your PCB from all sides. You often spot small (or big) things that can be improved. Do you see how close R2 is to the (footprint of the missing) Reset switch? The hole in the VBAT silk screen text?

And finally: always do a last DRC check before making Gerbers, and afterwards have a look at the Gerber files for obvious mistakes.

Even mor final remarks:

Your IMG_7395.JPG is quite dusty.

You can safely delete the backup files (LoPower2.bak, LoPower2.kicad_pcb-bak) and the netlist (LoPower2.net) from zip archives.