Hi, I’ve been looking at optimising the creation and application of IC Thermal Pads and would appreciate any feedback/advice/critisism.

I was looking for a modular way of creating Thermal Pads. This means that the Thermal Pad:

-

Is designed as a seperate entity to the actual Land Pattern where it is used.

-

Applies to Thermal Pads that can be seperated from the Land Pattern - i.e. it has a shape that is simple rectangle/square and not integrated into the Land Pattern.

The three parts of the Thermal Pad are: The copper pad, the thermal via(s) and solder paste.

The idea was to create a template for the thermal via + solder paste which is 1.00 mm2:

The Via is a PTH Pad, diameter 0.51 mm, Finished Hole size 0.25 mm.

The total paste area is 1.00 mm2, so minus the Finished Hole area, the paste area is 0.951 mm2.

As there should be 50% paste coverage, the actual pase area is 0.4755 mm2. This results in having 4 * 0.387 mm diameter paste pads per 1.00 mm2.

The Via has no mask/no paste.

The Pase Pads have no mask/no copper.

Net Pad Clearance: 0.000001 mm

There are guide marks on the corners for aligning multiple templates (comments layer).

The actual Thermal Pad is created by filling an SMD pad (mask/no paste, F.cu) with the template(s) above, lining up the guide marks. An SMD pad (mask/no paste, B.cu) is placed under the F.Cu pad.

The Module level Pad Clearance is 0.20 mm.

This means that the Thermal Pad dimensions are valid to the nearest mm.

The guide marks are then be removed in a text editor if required.

Gerber View Top:

Gerber View Bottom:

The Thermal Pad is placed under the applicable IC during Layout (non-real example):

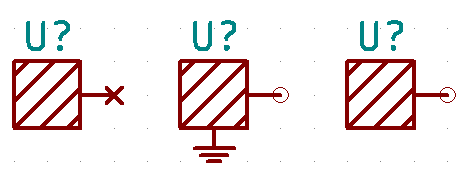

The Thermal Pads are represented on the schematic as:

I have not tried to use these yet as i have some doubts such as:

-

Is the pitch of the Thermal Vias too low (1.00 mm)?, examples on the web usually refer to 1.20 mm pitch which is quite a large difference at this level.

-

Would there be too many Thermal Vias at a pitch of 1.00 mm? Solder wicking problems etc.

-

Are the Paste Pads too small/too many?

-

Is it good practice to have seperate Thermal Pads or should they always be integrated into the Land Pattern?

Thanks,

Steev