I also had a look at the project…

First thing I noticed were a few stray wires on the schematic:

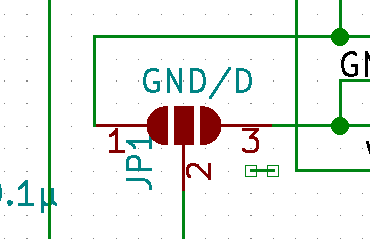

South-East of JP1:

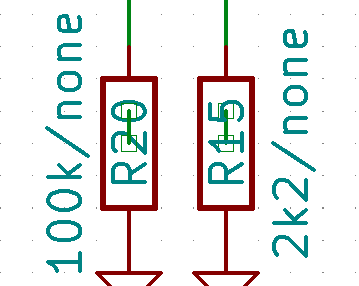

… and through both R15 and R20:

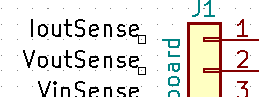

Then there are unconnected labels near J1 and J6:

And when running the ERC:

I get the “Pin connected to other pins, but not driven by any pin”

These can be fixed by adding PWR_FLAG symbols to your schematic.

There are some wires drawn though labels while there is plenty room to separate them, and this makes your schematic harder to read:

I’m also not a fan of those dashed lines. Usually they confuse more then they clarify.

Apart from that the schematic looks relatively neat. You even used the “No Connect” flags and probably have used the ERC.

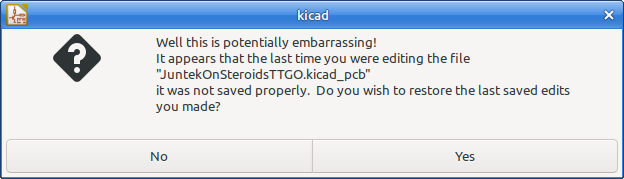

The version I got from github complained about:

So I clicked on

[ Yes ] to restore.

The version I’m reviewing may be slightly different from your latest revision.

DRC finds three errors:

It also finds two unconnected pins. All related to J61.

I got rid of both the errors and the unconnected pins by rotating J61 by 180 degrees. I sort of assume you already are / were aware of this.

I also do not like to draw zone boundaries on top of Edge.Cuts, and on top of each other.

I much prefer to make the zone outline look weird (such as pentagonal). This has three advantages. First, a zone is easy to select. and second, If anything goes wrong during Gerber creation, you see it immediately when inspecting the Gerbers.

Third: It’s easier to draw. No need for precise coordinates.

Something like:

Then I got the Idea to go back and do: Eeschema / Tools / Update PCB from Schematic [F8] and … oops. Your schematic and PCB are not in sync:

After the "Info: " lines, a bunch of "Connect: ", "Add: " and “Reconnect”. I cancelled this. I do not know your intentions, but schematic and PCB should be in sync before you make Gerbers and send them to be fabbed.

It’s also a good Idea to make a checklist with such things. Then, whenever in doubt, redo the checklist before you send out the Gerbers.

Your PCB is missing the KiCad logo. There are plenty to choose from

Just out of curiousity what would change, I did the Update PCB from Schematic [F8] thing. It added the missing footprint for fiducial FID2, but it did not cause further DRC violations. So It’s probably just some renamed nets or similar.

Then the GND plane…

This is a simple design and a GND plane is not terribly important, but still, ESP32 runs at 100+MHz and I saw a reference to an ADC1115 module. Which is a 16 bit ADC I believe (have not checked the datasheet).

Such is enough reason to take care of your GND plane, and getting into a habit to do the GND plane properly will make you a better PCB designer.

High frequency stuff such as switching logic adds a lot of noise all over a PCB, and this can be easily picked up by the ADC. You do have some smoothing capacitors (C1 through C4), but their location is far from optimal. Ideally you put these capacitors physically in between the connectors, and connect the other side of the capacitor directly to a clean area of the GND plane.

You are going from connector J21 (left) to J4 (middle), and then you add a piece of track to go to C3 (Upper Right corner):

Your row of capacitors may also look nice, but they’re quite vulnerable at the edge of the PCB. If you put them somewhere in the middle, they are protected from fingers and stuff bumping into them.

You’ve clearly chosen to make rows of your resistors for visual reasons, but this is quite bad from an electrical point of view. It complicates the routing and with that you cut what should have been your GND plane into little pieces. Having some pieces of copper connected to GND on one side of the PCB and also some on the other side do not add up to a GND plane.

GND planes are pretty complicated things (Yep, they are) but you can do it quite decent with a few simple rules:

- Use (as close as possible) layer dedicated as a continuous GND plane. Ideally that layer has no interruptions at all. small holes from via’s and THT footprints are acceptable, but not long tracks which cut the GND plane to pieces.

- Analyze how currents flow through the GND plane. Keep sensitive analog stuff far away from switching digital stuff. In your case it’s ideal to put C1 through C4 close to the GND pin of the ADC1115 adapter, then route the signal from one connector to the capacitor, and then back from the capacitor to the other connector.

- One GND plane is enough. It is not very useful to also add much GND on another layer. One good GND plane is much better then two layers, each with 3/4 GND.

- If it’s not possible to make a good GND plane, then at least stitch the pieces together with via’s (as a last resort option).

Your PCB will work (concerning the GND plane) as is, but you’ll probably pick up more noise then needed for the ADC.

Silkscreen text of “J4” and “C4” is overlapping. The line from J4 also overlaps with the text of R20 and R12. The J21 text is also overlapped with a line. Such things are easiest to view when you turn off all other layers, so only one Silkscreen layer is visible:

Your I2C lines do not have pullup resistors. These are mandatory. They may already be on the adapter boards, but sometimes those are quite weak. If you add them to your project too, then you can mount stronger pullups if needed (depending on bus capacitance).

I’m out of motivation for now. I have not looked at the Gerber files themselves.

[Edit:] Removed a faulty screenshot.